by legacy » 12 May 2012, 12:21

by legacy » 12 May 2012, 12:21

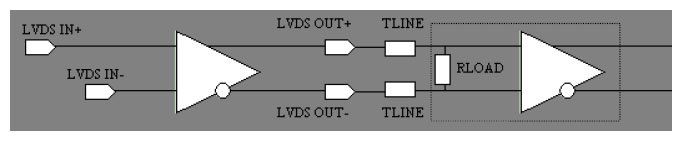

Solitamente quando si considerano le linee tra quadripoli si assume che l'impenza sia concentrata, cio' e' una approssimazione valida a basse frequenze dove l'impedenza della linea e' distribuita in modo uniforme lungo la stessa linea, ma all'aumentare della frequenza cioe' non e' piu' vero e nemmeno approssimabile perche' cambia spazialmente, e per frequenze ancora piu' alte (>1Ghz) l'approssimazione non solo cessa di essere anche solo vagamente valida, ma non risulta nemmeno piu' vera tutta la serie di assunzioni su cui si regge la legge di ohm.

Ai Ghz smettono di essere validi i principi di Kirchhof, cade la legge di ohm, per la ragione, in prima battuta, che i vettori di densita' di corrente non sono piu' una costante, la resistivita' non e' piu' costante perche' gli integrali che portano alla banale V = R * I non sono piu' validi, la R (integrale spaziale della resistivita') non e' piu' una costante, varia nello spazio e in funzione delle frequenza, degenerano in modo funzionale i fattori Q dei vari componenti reattivi che si palleggiano sempre energia reattiva ma con perdite non piu' trascurabili, oltre al fatto che ormai nei conduttori ci sono elettroni che oscillano a frequenze diverse, troppo diverse, tanto che si svuotano le parti di conduttore piu' profonde (effetto pelle) e si innescano persino fenomeni descivibili sono in termini di elettromagnetismo (chiedendo asilo alla relativita' e in certi strani casi chiedendo consulenza alla fisica quantistica)

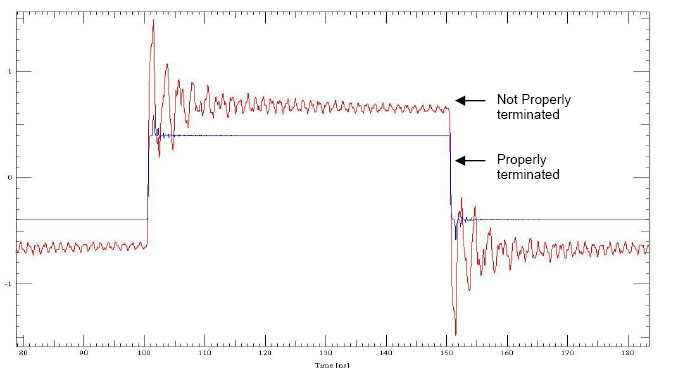

Tutto nasce dal fatto che per camibare lo stato logico da 0 ad 1, o da 1 a 0, quindi a livello fisico per mettere o togliere carica su un nodo, devi dari spedere energia per far crosscondurre i transistor che pompano o succhiano elettroni, e quando cio' succede si mettono in moto nuvole di elettroni che scorrono su un conduttore come l'acqua sul letto di un fiume, e per sonore botte di energia per muovere velocemente lo stato logico gli elettroni piu' esterni viaggiano molto piu' velocemente di quelli che stanno loro sotto e questo da luogo ad onde, onde di elettroni che viaggiano sopra ad altri elettroni con la stessa dinamica delle molecola d'acqua a volocita' diversa che descrivono le onde su, onde che viaggiano da un punto all'altro della linea, partono e rimbalzano indietro, e poiche' la corrente in un nodo e' data dalla somma delle cariche, e le cariche sono gli elettroni, ne consegue che se in un istante arriva un'ondata di elettroni in quel nodo c'e' piu' corrente istantanea, quindi un'impennata di tensione istananea, con conseguente risucchio e arrivo di altra ondata ... cioe' quelle cose bizzarre che mostra il DSO.

Restando ai Ghz il guaio e' che non solo ci sono onde, ci sono per natura degli elettroni anche fenomeni elettromagnetici tipici, per capirci, delle radio, ma c'e' anche una resisitiva' che non e' piu' costante non vale piu' la legge di ohm, a rigore quella resistivita' viene fuori da un integrale, e ora dall'integrale viene fuori una funzione che i vari simulatori son ben felici di macinare, ma non gli umani perche' ... e' un filo piu' tediosa per la mole di calcoli da fare.

Negli ordini delle 100,200,400Mhz le cose sono molto piu' tranquille, ma fino ad un certo punto, non c'e' piu' la pacchia che si ha sotto ai 50Mhz, dove ce la si cava con i software demo e un po' di accortezza nei pcb, sotto ai 12.5Mhz puoi anche andare di wirewrapping e se non sei troppo disordinato non hai problemi.

Dai 100Mhz in su' servono software molto potenti e costosi per queste simulazioni volte ad aiutare il masterista nello sbroglio del PCB che spesso (quasi sempre) trova la soluzione in uno sbroglio multi layer disegnando un PCB a diversi strati, 4, 6.

Last edited by

legacy on 12 May 2012, 13:18, edited 11 times in total.