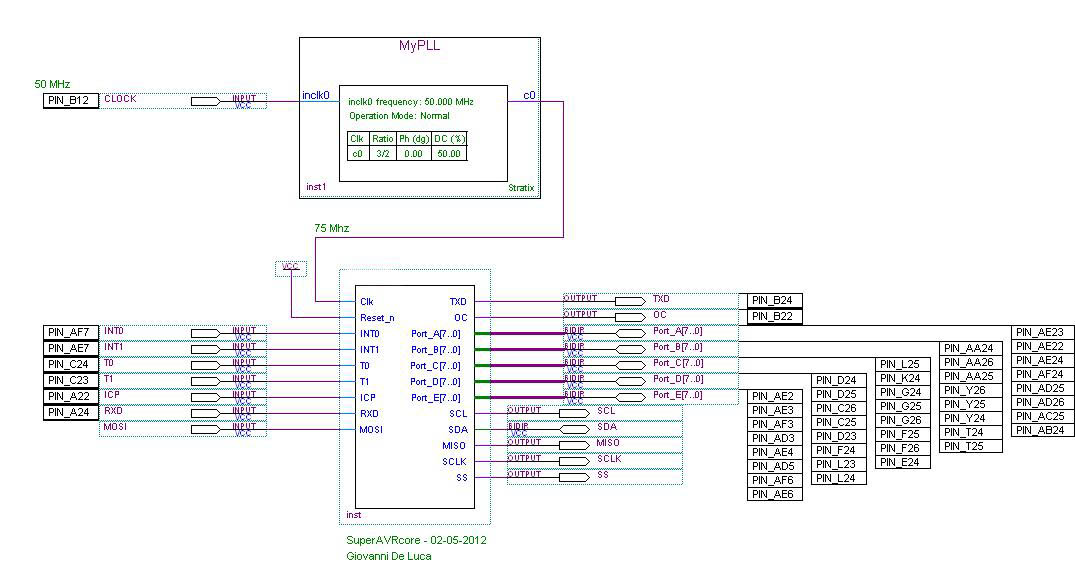

proprio qualche giorno fa, presso i Laboratori di Progettazione Elettronica dell' INFN di Catania, abbiamo completato con successo la sintesi di un SuperAVRcore, da impiegare nello slow-control di apparati elettronici durante esperimenti di fisica nucleare, con il quale è possibile emulare in buona parte i micro 8/16bit Risc AVR di Atmel. L'hardware è stato descritto interamente in (generic) VHDL ed è stato sintetizzato su una Fpga Stratix Altera 1S25F672C utilizzando 3251 Logic Element su 25660 disponibili, il (13%) delle risorose Hw. (Le altre risorse ci serviranno per implementare altre periferiche come ad esempio un CORDIC per calcoli trigonometrici veloci e un coprocessore per calcoli a virgola mobile).

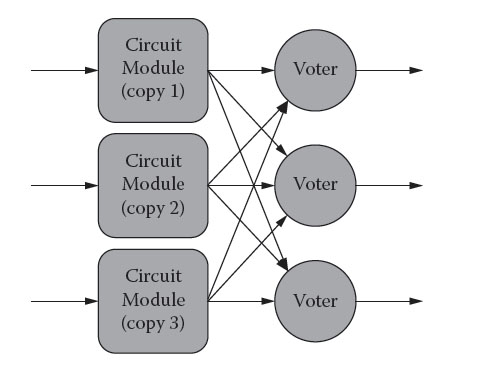

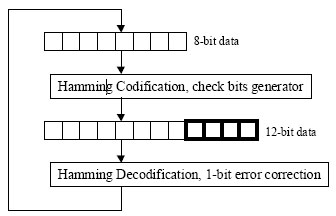

Abbiamo sviluppato il SoftCore con architettura Radiation Hardened implementando la codifica e decodifica Hamming per evitare fault per la presenza di bit-flips causati dalle radiazioni ionizzanti. La frequenza di clock a cui può lavorare il SoftCore AVR, è di circa 10 volte superiore degli AVR convenzionali. Possiamo tranquillamente superare i 100-150 Mips (dipende dalla FPGA impiegata). La possibilità di implementare molti micro uguali sullo stesso core utilizzando il "Triple Modular Redundancy" ed un Voter in uscita permette di avere una certezza sui risultati dei dati elaborati. Il passo successivo, visto che è possibile il porting del VHDL nativo, sarà quello di sintetizzare il core e gli altri IP in FPGA resistenti alle radiazioni ionizzanti della ACTEL.

Il top-level entity

Di seguito sono riportate alcune specifiche basilari del superAVRcore:

Core Freq > 150Mhz - 150MIPS with PLLx3 - Versione stabile 100Mhz

128K ROM sintetizzabile

32K RAM Hamming protected (espandibile fino a 64Kb)

5 porte I/O 8bit PA,PB,PC,PD,PE - <30 nSec toggle Time !!

UART 100% AVR compatible

Timer 16bit

Timer 8bit

Input ICP

Input T0 e T1

Fast PWMout 10bit - 40Khz

I2C TWI - 100 / 400 Khz

SPI - up-to 8 Mbit/sec

External Interrupts Int0 e Int1

Compatibilità 100% con il firmware per AVR Atmel, tools used: AVRstudio, Wiring, WinAVR, AVR-GCC, Bascom-AVR, Codevision, ICC ed altri.

Ultimo aggiornamento - 3/05/2012